Serious about FPGA design? Don’t forget verification!

Our friends from Bitvis are giving another course – this time in Stockholm. We are not making any money on this, but you should know about it for two reasons:

- We know it’s a damn good course

- If you have big FPGA’s in your design, you should go to our SI Week as well 🙂

This course aims to significantly reduce the verification time while at the same time improving the product quality. This is not only possible, – but in fact easily achievable in almost every FPGA development project. All it takes is a bit more structure in your verification environment. No expensive tools, and no expensive IP, – just a better verification approach.

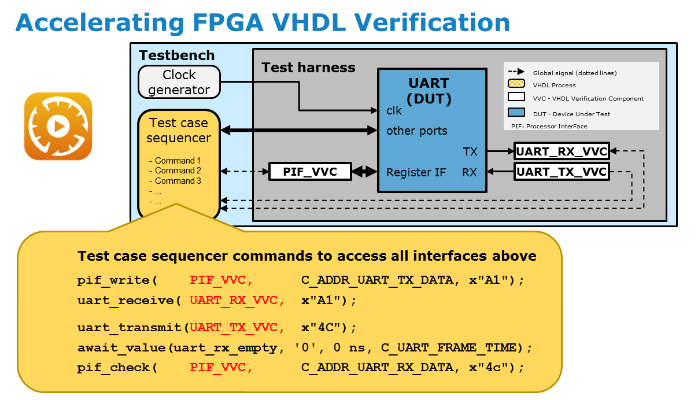

Overview: Anyone writing test cases should have a good overview of the testbench (TB) architecture, how to control it and how everything is connected

Readability: The test sequencer should be easy to understand by anyone – preferably like a simple SW sequencer resembling the verification specification

Simplicity and abstraction: It must be easy to control DUT stimuli and check DUT outputs – in most cases also for simultaneously active interfaces.

Extendability and Maintainability: As specifications often changes, and as you want to have concurrent design and verification – it must be easy to modify test cases and add new tests and functionality.

It must also be easy to make variants, and for new designers to very fast be able to modify or improve the TB environment

Reuse: Efficient reuse within a single project is important between module TBs and from module TBs to an FPGA TB.

Efficient reuse between projects would then just be a free bonus.

It is pretty obvious that the issues above are critical for both efficiency and quality. The good thing is that you get both efficiency and quality at the same time. The bad thing is that the huge majority of testbenches are not even close to these targets. So – the challenge is how to achieve this – and that is what this course is all about.

The course will explain what is needed as a general approach to make structured TBs that do actually meet all these targets. UVVM is free and open source – and will be used to show practical examples. The course will also show how you can build your own BFMs, Verification components, test sequencer commands, etc.

For registration and more information please go to Bitvis.

SI Week in Copenhagen

M.Sc.EE, SI Consultant

M.Sc.EE, SI Consultant